我正在使用 Verilog 设计一个类似 MIPS 的 CPU,现在我正在处理数据危险。我有这些指示:

Ins[0] = LW r1 r0(100)

Ins[1] = LW r2 r0(101)

Ins[2] = ADD r3 r2 r1

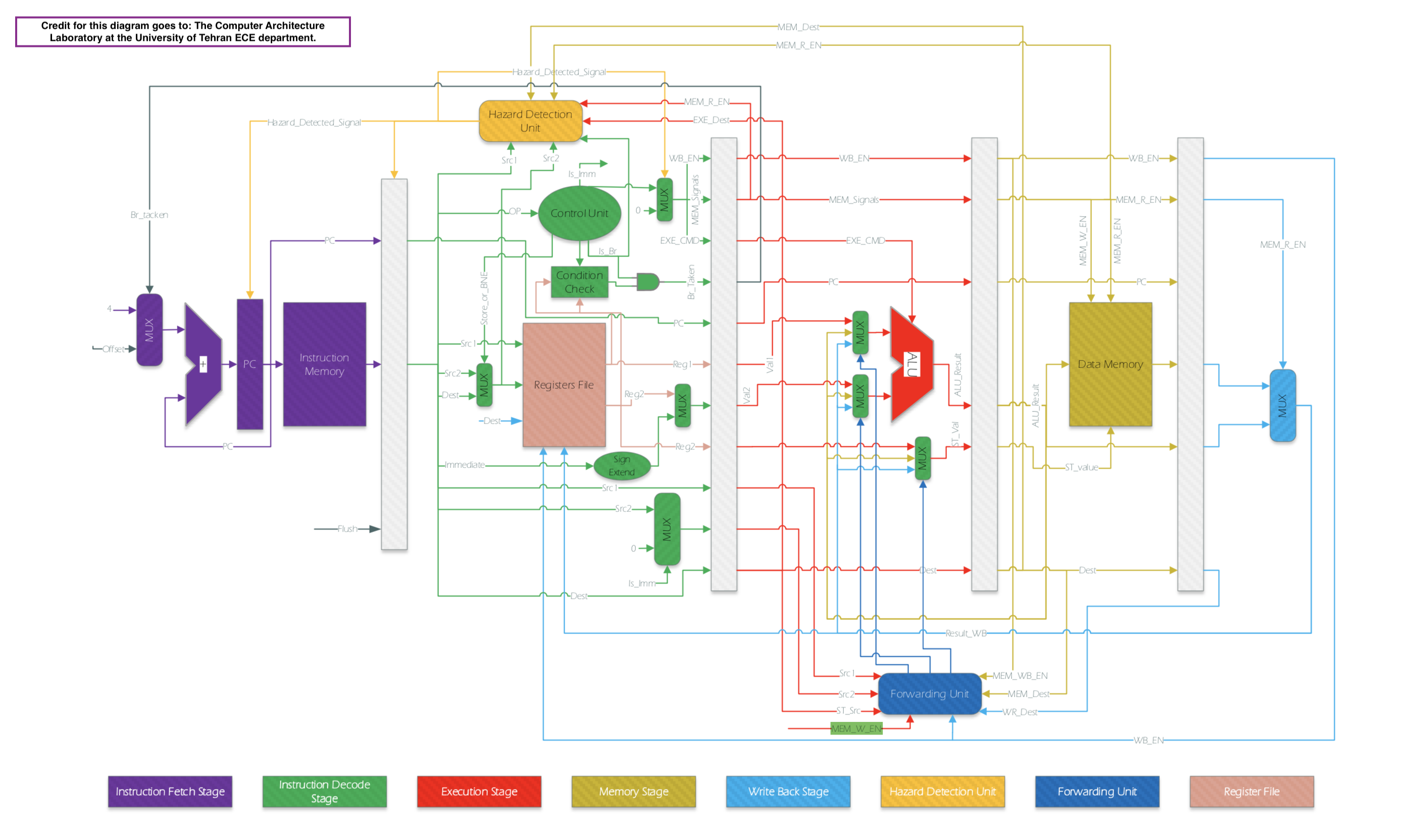

我正在使用管道,我的 dataPath 是这样的:

我有 5 个阶段,有 4 个锁存缓冲区将它们分开。

我有 5 个阶段,有 4 个锁存缓冲区将它们分开。

问题是当 ADD 指令到达 stage3(ALU 应该计算 r1 + r2)时,指令 1(第二个 LW)处于 stage 4 并且还没有读取内存的 r0 + 101 地址,所以我应该停止一个周期,然后 Ins1 到达最后阶段。

在这种情况下,第一个 LW 已完成工作,并且 r1 的新值不在 dataPath 中的任何位置,但我需要将此值传递给 ALU 的输入 B。

(这被称为数据转发,因为当第三条指令处于阶段 2 时,r1 的值还没有准备好,我应该从后面的阶段转发它(从最后一个 MUX 出来并进入 ALU MUX 的蓝线),但是因为在第二个 LW 的失速中,我没有 r1 的值。

谢谢你的帮助。