虽然我已经完成了数字逻辑的大学课程,但我是 VHDL 设计的新手,我希望有人可以帮助我创建 2 个依赖于彼此状态的时钟信号。

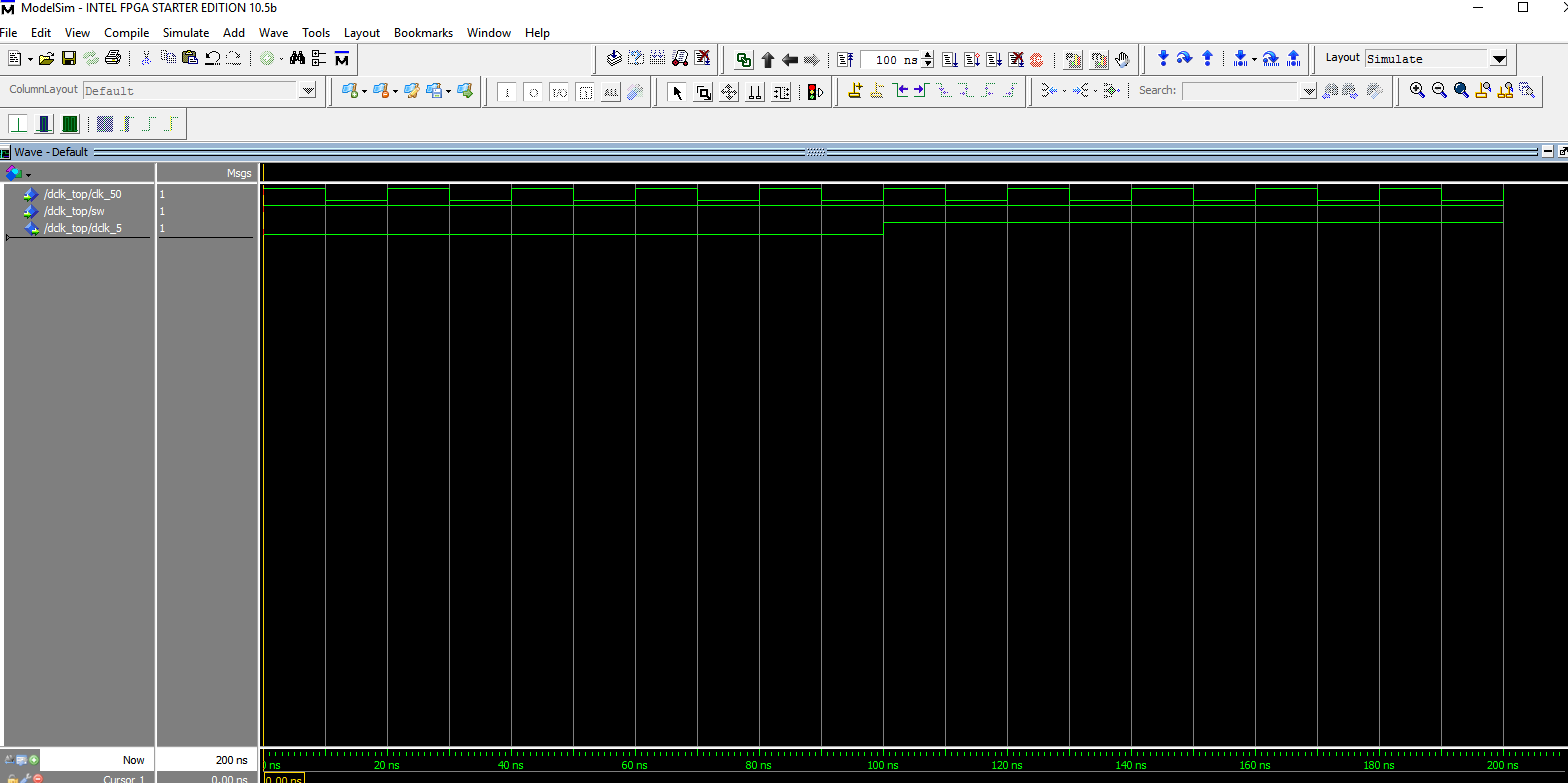

我在 DE2-115 FPGA 板上使用 50 MHz 时钟,用于创建 5MHz 时钟(名为 dclk_5)。但是,模拟显示了两个信号,但运行时间仅为 200 ns,并且不再运行。为什么仿真运行时间不超过 200 ns?

2个时钟的数据表:

用于测试合成但仿真不正确的 dclk_5 和 clk_50 的替代 VHDL 设计:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity DCLK_top is

port(

clk_50 : in std_logic;

sw : in std_logic;

dclk_5 : out std_logic

);

end DCLK_top;

architecture behaviour of DCLK_top is

signal clk_counter : integer range 0 to 10 := 0;

signal dclk_counter : integer range 0 to 8 := 0;

signal dclk_pause_counter : integer range 0 to 7 := 0;

signal dclk_pause : std_logic := '0';

signal clk_pause_counter : integer range 0 to 7 := 0;

begin

dclk_proc : process(clk_50)

begin

if(clk_50'event and clk_50='1' ) then

clk_counter <= clk_counter+1;

if(clk_counter=10) then

clk_counter <= 0;

end if;

if(clk_counter<5) then

dclk_5 <= '0';

else

dclk_5 <= '1';

end if;

end if;

end process dclk_proc;

end architecture behaviour;

仿真图片: